Einleitung

Auf der WinHEC, Microsofts Entwicklerkonferenz für Hardware, hat die „Arapahoe“ Arbeitsgruppe um Intel, Microsoft und den großen Herstellern Compaq, Dell, IBM und HP den ersten Entwurf für die Spezifikation von PCI Express zur Diskussion vorgelegt. Der Entwurf wird nun in der “PCI Special Interest Group“ (PCI-SIG) nachbearbeitet. Die Veröffentlichung der abgeschlossenen Spezifikation wird für Ende des 2. Quartals 2002 erwartet.

PCI Express war vormals als Third Generation I/O (3GIO) bekannt und wurde mit dem Ziel entwickelt, den für Datentransfers innerhalb des Computers derzeit meist eingesetzten PCI 2.2 Bus zu ersetzen.

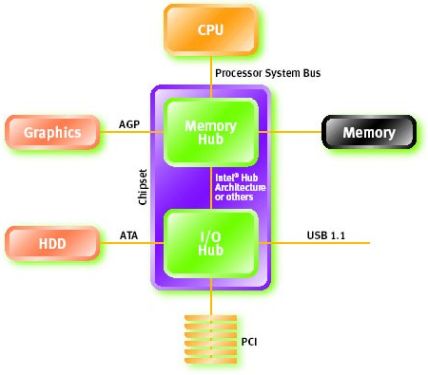

Aktuelle Architektur

Die jetzige Form von PCI (PCI 2.0 bis 2.2) besteht bereits seit 10 Jahren und stößt zur Zeit in der Leistungsfähigkeit mit der bei 32bit/33MHz auf 133MB/s begrenzten Datenrate an ihre Grenzen. In der Praxis werden nur knapp 100MB/s erreicht. Moderne Schnittstellen wie Gigabit Ethernet, schnelle Massenspeicherschnittstellen wie ATA-133 und Ultra160-SCSI lasten damit den gewöhnlichen PCI Bus bereits voll aus, so dass es schnell zu Engpässen kommt und die Gesamtleistung sinkt. Eine Möglichkeit bietet PCI 2.2 jedoch mit der Erweiterung auf eine Breite von 64bit und/oder 66MHz Arbeitsfrequenz. Dadurch steigen jedoch die Kosten enorm, so dass diese Alternative nur im Serverbereich wirtschaftlich erscheint. Hier setzt die neue PCI Express Spezifikation an.

Neueste Kommentare

16. April 2025

15. April 2025

14. April 2025

14. April 2025

14. April 2025

14. April 2025