Smart Memory Access & Advanced Digital Media Boost

Speicherzugriffe benötigen Zeit. Es wird daher versucht, Daten möglichst früh in den Cache zu laden. Hierbei wird sozusagen spekulativ in die Zukunft vorgegriffen. Der mögliche Weg eines Programmes wird in Zeiten geringerer Auslastung bereits durchgespielt und möglicherweise benötigte Ergebnisse werden berechnet und zwischengespeichert. Wenn das Programm dann tatsächlich an der Stelle angekommen ist, an der ein ensprechendes Ergebnis benötigt wird, so werden die gespeicherten Ergebnisse ausgelesen und das benötigte übergeben. Die restlichen werden verworfen. Dies klingt zwar nach großem Mehraufwand, rentiert sich aber, da der Prozessor ja mehrere Befehle gleichzeitig ausführen kann und dadurch keine “Schlafphasen” geopfert werden. Intels “Smart Memory Access” stellt Algorithmen bereit, die eine möglichst konfliktfreie Vorausplanung mit einem Minimum an illegalen Zugriffen zum Ziel hat. Wenn doch auf die falschen Speicherbereiche zugegriffen wird, sorgt ein Algorithmus dafür, dass die Instruktion mit erlaubten Daten neu ausgeführt wird. Zusätzlich werden in der Intel Core Mikroarchitektur zwei Prefetcher pro L1 und L2 Cache eingesetzt.

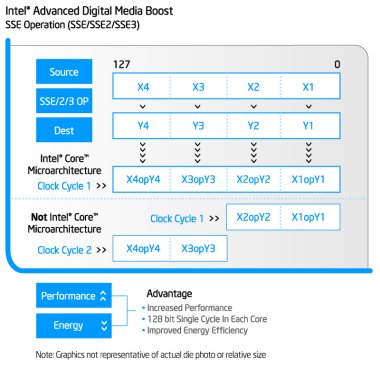

Die Busbreite der SSE-Einheiten wurde auf 128bit erhöht. SSE/2/3-Befehle, die bisher in zwei Taktzyklen abgearbeitet wurden, benötigen jetzt nur noch einen Zyklus. Programme, die in hohem Maße auf SSE/2/3-Befehle setzen, können dadurch einen deutlichen Performance-Gewinn erzielen. Getauft wurde diese Verbreiterung “Advanced Digital Media Boost”.

Neueste Kommentare

14. Januar 2025

14. Januar 2025

31. Dezember 2024

28. Dezember 2024

27. Dezember 2024

27. Dezember 2024